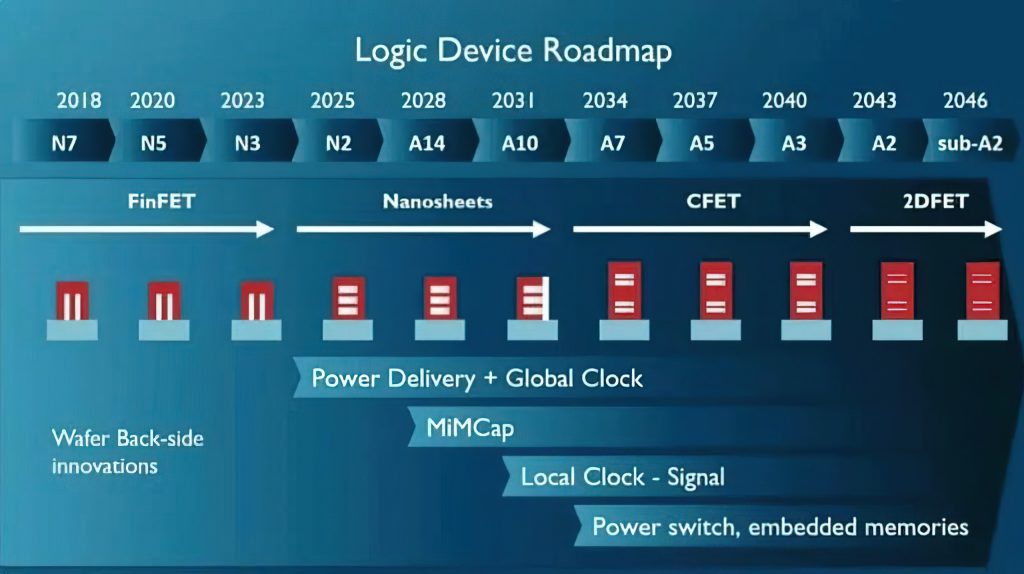

بسیاری از کارشناسان از اشباع قانون مور و محدودیتهای فیزیکی سیلیکون صحبت میکنند، اما مؤسسه تحقیقاتی IMEC بلژیک با انتشار یک نقشهراه جالب، افقهای جدیدی را برای صنعت نیمهرسانا متصور شده است. طبق این گزارش، اگرچه سرعت رشد چگالی ترانزیستورها نسبت به دهههای گذشته کاهش یافته، اما فناوریهای نوینی همچون CFET و ترانزیستورهای دو بعدی (2D FET) مسیر رسیدن به گرههای زیر ۱ نانومتر را هموار میکنند. انتظار میرود اولین تراشههای ۰.۷ نانومتری در سال ۲۰۳۴ و گرههای فوقپیشرفته ۰.۲ نانومتری تا سال ۲۰۴۶ به مرحله تکمیل توسعه برسند.

صنعت تولید تراشه درحال ورود به «عصر آنگستروم» است، اما این پیشرفت به سادگی به دست نمیآید. هزینه تولید گرههای جدید به دلیل نیاز به تجهیزات لیتوگرافی فوق پیشرفته و گرانقیمت، بسیار صعودی است. به همین دلیل، صنعت نیمهرسانا به سمت راهکارهای جایگزین مانند چیپلتها و بستهبندی پیشرفته کوچ کرده است. این روشها اجازه میدهند بهجای تغییر مداوم گرههای تولیدی، با ترکیب هوشمندانه قطعات مختلف، به کارایی بالا و قیمت مناسب دست یافت.

اما اصلاً آنگستروم چیست؟ در صنعت نیمهرسانا، واحد اندازهگیری تراشهها برای دههها نانومتر بوده است. هر نانومتر برابر با یکمیلیاردم متر است. اما با کوچکتر شدن ترانزیستورها به ابعادی کمتر از ۱ نانومتر، دانشمندان به واحد کوچکتری به نام آنگستروم (Å) روی آوردهاند.

نقشه راه صنعت نیمهرسانا و فرایند تولید تراشهها

طبق نقشه راه IMEC، در بازه زمانی فعلی و تا سال ۲۰۳۱ تمرکز اصلی صنعت بر تکامل فناوری نانوشیتها و گذر از گرههای ۲ نانومتر به سمت ۱ نانومتر معطوف میشود. غولهای بزرگ فناوری مثل TSMC و اینتل رقابت شدیدی را برای فرمانروایی بر این مرحله آغاز کردهاند.

شرکت TSMC امسال با معرفی N2 که از ترانزیستورهای نانوشیت با ساختار GAA بهره میبرد، قدم اول را برداشته است و انتظار میرود گرههای بهینهتری مانند A16 و A14 نیز تا سالهای آتی وارد مدار شوند. در جبهه آبیها، اینتل با گره 14A و نسخههای بهینهسازیشده آن قصد دارد جایگاه خود را بازیابی کند. این دوره از پیشرفت که با گره A10 در حدود سال ۲۰۳۱ به اوج خود میرسد، آخرین مرحله از معماری کلاسیک نانوشیت خواهد بود و سپس در آستانه ورود به دنیای شگفتانگیز زیر ۱ نانومتر قرار میگیریم.

تحول بنیادین واقعی در سال ۲۰۳۴ با معرفی معماری ترانزیستورهای مکمل یا CFET آغاز خواهد شد. در این فناوری انقلابی، مهندسان بهجای چیدن ترانزیستورها در کنار هم، آنها را به صورت عمودی بر روی یکدیگر انباشته میکنند. این رویکرد جدید باعث میشود مساحت اشغالشده توسط سلولهای منطقی بسیار کاهش و چگالی ترانزیستورها در مدارها تا ۸۰ درصد افزایش یابد.

طبق برنامهریزیهای انجامشده، اولین تراشههای زیر ۱ نانومتر با گره ۰.۷ نانومتری (A7) در سال ۲۰۳۴ متولد میشوند و پس از آن در فواصل زمانی معین، گرههای ۰.۵ نانومتری در سال ۲۰۳۶ و ۰.۳ نانومتری در سال ۲۰۴۰ به مرحله تکمیل توسعه خواهند رسید تا مرزهای قدرت پردازشی را جابهجا کنند.

اما نهاییترین افق پیشبینیشده در این نقشه راه، دسترسی به فناوری ترانزیستورهای دوبُعدی (2D FET) در اواسط دهه ۲۰۴۰ میلادی است. در این مرحله، سیلیکون جای خود را به مواد نوین دو بعدی میدهد که اجازه میدهند ساختارهای CFET یا نانوشیتها در ابعادی به اندازه ۲ آنگستروم یا همان ۰.۲ نانومتر ساخته شوند. انتظار میرود گره A2 در سال ۲۰۴۳ و نسخههای زیر ۰.۲ نانومتری در سال ۲۰۴۶ معرفی شوند.

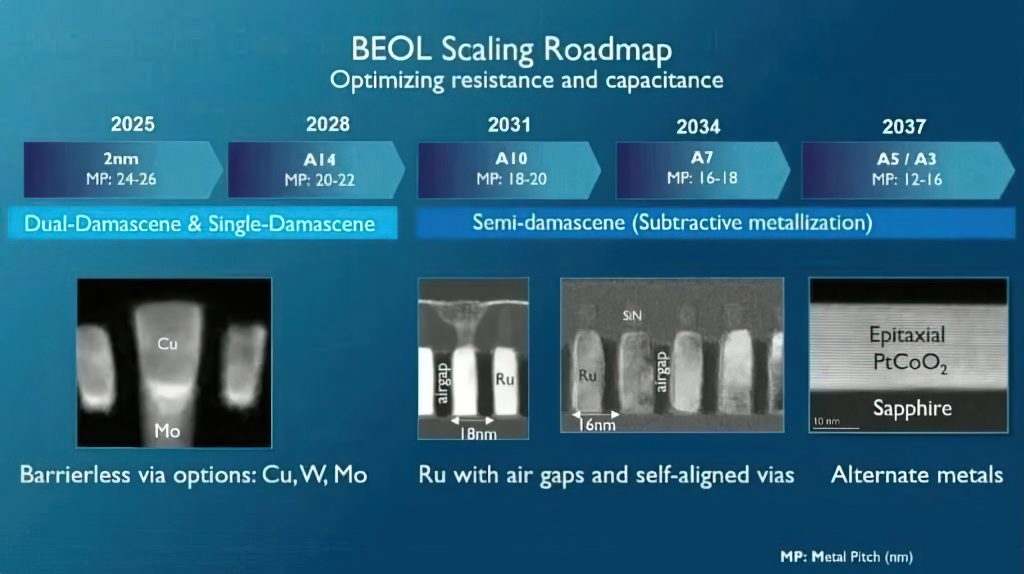

موازی با تغییر ساختار ترانزیستورها، سیستمهای اتصال و انتقال توان نیز باید بازنگری شوند. در بخش اتصالات داخلی (BEOL)، به دلیل ناتوانی مس در انتقال پایدار جریان در ابعاد زیر نانومتر، فلز روتنیوم جایگزین خواهد شد که با ایجاد شکافهای هوایی و لایههای بدون سد، مقاومت الکتریکی را کاهش و رسانایی را افزایش میدهد. حتی در گرههای ۰.۵ نانومتر، استفاده از مواد بسیار خاصی مانند اکسید کبالت پلاتین بر روی بستر یاقوت کبود برای کاهش حداکثری مقاومت در دستور کار است.

نظرات کاربران